您現在的位置是:首頁 >動態 > 2020-12-02 09:08:22 來源:

基于3D憶阻器的電路用于大腦啟發式計算

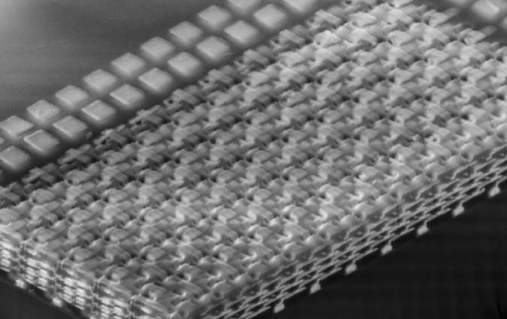

馬薩諸塞州大學和空軍研究實驗室信息局的研究人員最近創建了一種3-D計算電路,該電路可用于映射和實現復雜的機器學習算法,例如卷積神經網絡(CNN)。這種3D電路發表在《自然電子》上的論文中,由8個憶阻器層組成。調節電路中電流并直接在硬件中實現神經網絡權重的電氣組件。

“以前,我們開發了一種非常可靠的憶阻設備,可以滿足人工神經網絡內存中計算的大多數要求,將這些設備集成到大型二維陣列中,并展示了多種機器智能應用,”夏強飛教授說。進行這項研究的研究人員中的一位告訴TechXplore。“在我們最近的研究中,我們決定將其擴展到第三維,探索3-D神經網絡中豐富連接的好處。”

基本上,夏教授和他的團隊能夠通過實驗演示具有八個憶阻器層的3-D計算電路,這些電路都可以參與計算過程。它們的電路與其他先前開發的3-D電路(例如3-D NAND閃存)有很大不同,因為這些系統通常由堆疊的具有不同功能的層(例如,傳感器層,計算層,控制層等)組成或粘合在一起。

“嘗試構建多層計算電路時先前遇到的主要挑戰之一是,除憶阻器外,沒有其他可堆疊的設備,并且能夠保持計算所需的所有性能,”彭林說。進行這項研究的研究人員告訴Techxplore。“例如,基于硅的CMOS技術是主流計算芯片的基本構建塊,但是眾所周知,它依賴于不可堆疊的高質量單晶硅層,因此很難用于3-D電路。”

盡管憶阻器是出色的堆疊設備,但迄今為止,研究人員仍無法實現用于大型計算應用的具有多個堆疊憶阻器層的3D電路。實際上,構建這樣的電路需要高度復雜的過程,并且需要使用可以克服在執行大規模陣列操作時通常遇到的挑戰的技術。

“建立憶阻器陣列的主要問題之一是單元間干擾,即所謂的'潛行路徑問題,”這源于每個類似電阻的憶阻器元件之間的無源連接,” Lin說。“ A 2 -D憶阻器陣列可以通過將晶體管作為選擇器件來緩解此問題,但是該解決方案無法應用于3-D。結果,現有的基于完全連接的拓撲結構的3D憶阻器設計在擴展到大型3D網絡時將遭受越來越多的泄漏。”

為了克服以前嘗試開發基于憶阻器的3D電路進行大規模計算時所面臨的挑戰,研究人員設計了一種具有獨特拓撲結構(即各個零件的布置)的電路。憶阻器在其電路中通過“本地連接”鏈接。這意味著每個憶阻器僅與附近的少數設備共享電極,這種獨特的設計策略可抑制大多數潛行路徑,最終實現大規模數組運算。

夏,林教授及其同事設計的電路中,憶阻器的布置和連接的獨特方式也使其成為實施先進計算技術(如人工神經網絡(ANN))的理想選擇。過去的研究表明,基于憶阻器的系統可以直接托管ANN,數據在其電路中流動,并可以實現網絡的向前/向后傳播策略。但是,幾乎所有現有的憶阻器陣列都以規則形狀的交叉開關結構排列,這不能反映ANN的結構。